Index

Page 5 of 10

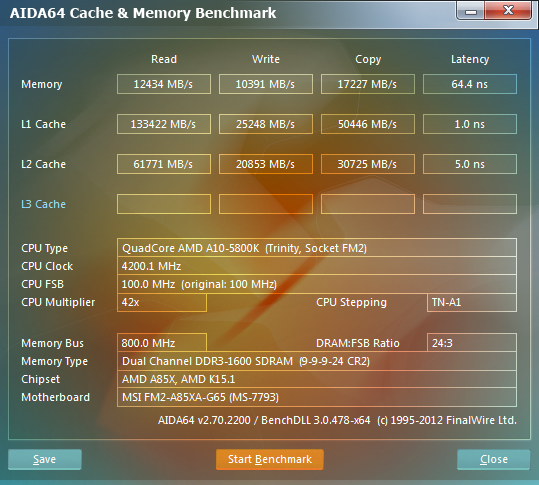

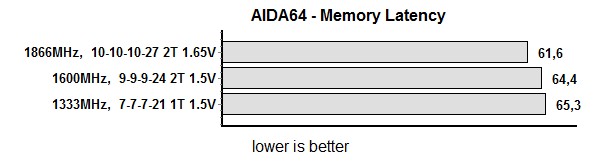

This benchmark measures the typical delay when the CPU reads data from system memory. Memory latency time means the penalty measured from the issuing of the read command until the data arrives to the integer registers of the CPU. The code behind this benchmark method is written in Assembly, and uses 1 MB alignment, 1024-byte stride size. Memory is accessed in forward direction.

Memory Latency benchmark test uses only the basic x86 instructions and utilizes only one processor core and one thread.

We can't confirm this but AIDA64 discussion forum leaked a piece of info claiming AIDA64 will soon completely drop all current memory benchmarks.